Ubuntu ic f321 usb 2.0 serial full#

To reduce the total system cost and enhance the overall functionality, Exynos4412 includes many hardware peripherals, such as a TFT 24-bit true color LCD controller, camera interface, MIPI DSI, CSI-2, a system manager for power management, embedded GPS and GLONASS, MIPI slimbus interface, MIPI HSI, four UARTs, 24-channel DMA, timers, general I/O Ports, three I2S, S/PDIF, eight IIC-BUS interfaces, three HS-SPI, USB Host 2.0, and USB 2.0 devices operating at high speed (480Mbps), two USB HSIC, four SD Host and a high-speed Multimedia Card interface, a chip to chip interface, and four PLLs for clock generation.Ī package on package (POP) option with MCP is available for small form factor applications. USB 2.0 compliant full speed with LPM L1 supported. The static memory port supports NOR flash and ROM type external memory and components. The dedicated DRAM ports support the LPDDR2 interface for high bandwidth. The memory system has dedicated DRAM ports and a static memory port. The hardware encoder/decoder supports real-time video conferencing and digital TV out. This will be the case if you’re using an Omega2 or Omega2+ on an Expansion Dock or Mini Dock, or an Omega2S or Omega2S+ in the Omega2S Development Kit board.

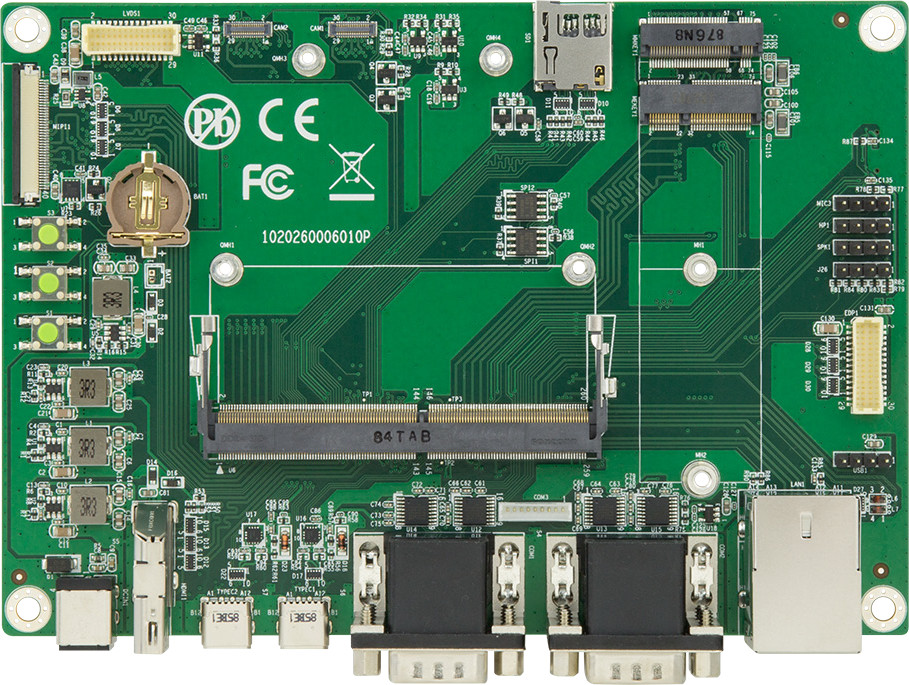

Ubuntu ic f321 usb 2.0 serial driver#

This compact USB 3.0 network adapter is backward compatible with older USB 2.0/1.x computer systems (speed limited by USB bus), making it. The Omega’s command prompt can also be accessed with a USB cable, as long as the Omega’s UART0 is connected to a USB-to-Serial device. 1.6 0.831744 tun: (C) 1999-2004 Max Krasnyansky <> 0.835020 PPP generic driver version 2.4.2 0.836242 ehcihcd: USB 2.0.An integrated Multi Format Codec (MFC) supports encoding and decoding of MPEG-2/4, H.263, H.264 and decoding of VC1. The USB31000S USB 3.0 to Gigabit Ethernet Adapter adds a single RJ45 Ethernet port to a USB-enabled computer system, with support for Gigabit network connections at full bandwidth, unlike USB 2.0 adapters. These tasks, for example motion video processing, image signal processing, display control and scaling. Exynos4412 adopts a 64-bit/128-bit internal bus architecture and many powerful hardware accelerators for different tasks. It has been built to provide optimized hardware performance for the mobile telecommunication services and general applications on smart phones. Builtin front parallel 1.3M pixel and rear MIPI 5M pixelĦ (4 proved by LAN9514, 2 proved by USB3503)Įxynos4412 is a 32-bit RISC cost-effective, low power, performance optimized Cortex-A9 Quad Core based micro-processor solution for smart phone applications.